Главная страница Случайная лекция

Мы поможем в написании ваших работ!

Порталы:

БиологияВойнаГеографияИнформатикаИскусствоИсторияКультураЛингвистикаМатематикаМедицинаОхрана трудаПолитикаПравоПсихологияРелигияТехникаФизикаФилософияЭкономика

Мы поможем в написании ваших работ!

Узлы цифровых устройств

Узлы цифровых устройств – это функционально законченные устройства, в состав которых входит некоторое количество (от единиц до нескольких сотен) электронных элементов. Узлы выполняют функции, которые широко используются при построении сложных цифровых дискретных устройств. Рассмотрим законы функционирования этих устройств и их схемы.

8.1. Дешифраторы

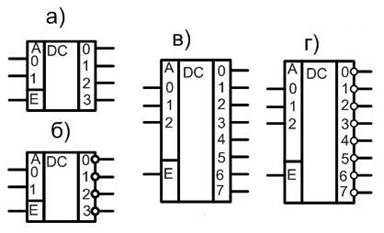

Дешифратор – это устройство, которое преобразует двоичный n-разрядный код в 2n-разрядный унитарный двоичный код. Унитарным кодом называется такой двоичный код, у которого состояние одного двоичного разряда противоположно состоянию всех остальных разрядов, т. е. если все разряды равны 0, то только один разряд равен 1. Таким образом, дешифратор имеет n входов и 2n выходов. Дешифраторы обозначаются латинскими буквами DC (декодер). Разрядность дешифратора считается по числу входных переменных. Так, при n=2 дешифратор называется двухразрядным, при n=3 трехразрядным и т. д. Если DC имеет 2n выходов, то он называется полным, в противном случае неполным. Например, двухразрядный полный DC может формировать на выходах один из следующих кодов: 1000, 0100, 0010, 0001. Такой DC называется DC с прямыми выходами. Если DC формирует на выходе коды 0111, 1011, 1101, 1110, то он называется инверсным. На схемах дешифраторы обозначают так, как показано на рис. 8.1.

Рис. 8.1. Обозначения дешифраторов:

а – полный двухразрядный DC с прямыми выходами;

б – полный двухразрядный DC с инверсными выходами;

в – полный трехразрядный DC с прямыми выходами;

г – полный трехразрядный DC с инверсными выходами

Выход, имеющий противоположное по отношению к остальным выходам значение, называется возбужденным.

В обозначениях дешифраторов различают несколько полей:

¨ n-разрядное адресное поле (обозначено буквой А) показывает, сколько разрядов имеет входной код, где цифры 0 и 1 показывают вес разряда двоичного кода (0 – младший разряд, 1 – старший разряд кода и т. д.);

¨ выходное поле (обозначений может не иметь) содержит 2n выходов. Выходные функции дешифратора с инверсными выходами обозначаются инверсиями;

¨ поле Е – поле управляющего входа может присутствовать (рис. 8.1) или отсутствовать (рис. 8.6, б), и тогда его в обозначении DC опускают. Назначение этого входа рассмотрено ниже. На рис. 8.2 приведены таблица истинности DC, изображенного на рис. 8.1 (а) и БФ всех его выходов. На рис. 8.3 приведены таблица истинности DC, изображенного на рис. 8.1 (б) и БФ всех его выходов.

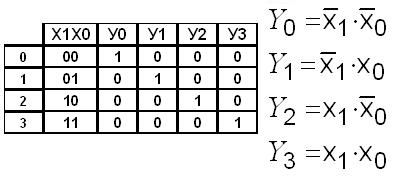

Рис. 8.2. Таблица истинности и булевы функции выходов двухразрядного дешифратора с прямыми выходами

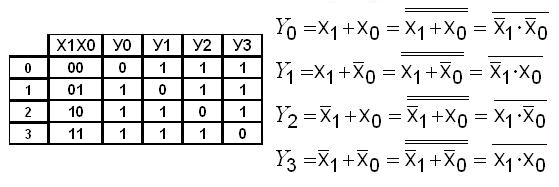

Рис. 8.3.Таблица истинности и булевы функции выходов двухразрядного

дешифратора с инверсными выходами

При поступлении на вход дешифратора двоичного кода 00 (0 десятичного кода) возбуждается выход 0, при поступлении кода 01 (1) возбуждается выход 1 и т. д.

В таблице истинности DC, в любом столбце k (рис. 8.2) только одна единица, а в табл. 8.3 только один ноль, т. е. функция Yk фактически описывается конституентой единицы для дешифратора с прямыми выходами и конституентой нуля для дешифратора с инверсными выходами. Схемы дешифраторов представлены на рис. 8.4 (а) и рис. 8.4 (б).

Рис. 8.4. Схемы двухразрядных дешифраторов:

а – с прямыми выходами; б – с инверсными выходами

Введем еще одну переменную Е, на которую умножим булеву функцию каждого выхода DC:

Рис. 8.5. Схемы управляемых дешифраторов:

а – с прямыми выходами; б – с инверсными выходами

При Е=0 У0=У1=У2=У3=0 (рис. 8.5, а), а при Е=1 функции выходов принимают значения в зависимости от входного кода. Вход Е называют управляющим входом или входом стробирования. При Е=0 дешифратор «выключается», т. е. все выходы неактивны, а при Е=1 «включается» в работу. Такие дешифраторы называют управляемыми. Схемы управляемых дешифраторов представлены на рис. 8.5.

В цифровых устройствах принято так строить узлы, чтобы на основе малоразрядных устройств можно было строить многоразрядные. Продемонстрируем это на примере двухразрядного дешифратора.

Задача 8.1. Построить дешифратор трехразрядного двоичного кода на двухразрядных управляемых дешифраторах.

Для решения задачи сначала рассмотрим таблицу истинности трехразрядного дешифратора (табл. 8.1):

Таблица 8.1.

Таблица истинности трехразрядного дешифратора

| Х1 | Х2 | Х3 | У0 | У1 | У2 | У3 | У4 | У5 | У6 | У7 | |

Запишем систему булевых функций выходов дешифратора:

Переобозначим переменные  , перепишем систему функций и преобразуем таблицу истинности:

, перепишем систему функций и преобразуем таблицу истинности:

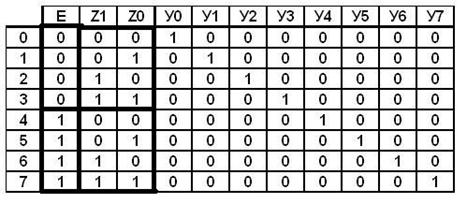

Таблица 8.2

Преобразованная таблица истинности трехразрядного

дешифратора

Анализ табл. 8.2 показывает, что переменные z1 и z0 в верхней и нижней части таблицы принимают одни и те же значения. Поэтому их можно подать на адресные входы А0 и А1 двухразрядных дешифраторов. При поступлении на входы одинаковых комбинаций z1 и z0 у обоих дешифраторов будут возбуждаться одни и те же выходы. Но если на управляющий вход дешифратора DC1 подать инверсную переменную  , а на вход DC2 прямую переменную Е, то:

, а на вход DC2 прямую переменную Е, то:

¨ при Е=0 DC2 отключится, т. е. У4=У5=У6=У7=0, но выходы DC1 будут возбуждаться в соответствие с кодами z1z0, т. к.  ;

;

¨ при Е=1, наоборот, отключится DC1 У0=У1=У2=У3=0, DC2 будет работать в соответствие с кодами z1z0.

Схема включения дешифраторов показана на рис. 8.6 (а), на рис. 8.6 (б) показано обозначение трехразрядного неуправляемого дешифратора, построенного на двух двухразрядных дешифраторах в соответствии с табл. 8.1.

Рис. 8.6. Схема и обозначение трехразрядного дешифратора:

а – схема трехразрядного дешифратора, собранного из двухразрядных дешифраторов; б - обозначение трехразрядного дешифратора на схемах

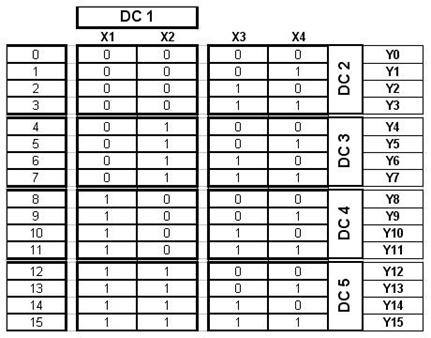

Задача 8.2.Построить схему четырехразрядного дешифратора двоичного кода на дешифраторах меньшей разрядности. Для решения задачи с помощью двухразрядных дешифраторов преобразуем таблицу истинности следующим образом (рассмотрим только левую часть таблицы).

Из табл. 8.3 видно, что дешифраторы DC2, DC3, DC4, DC5 дешифрируют одинаковые коды переменных х3х4. Дешифратор DC1 декодирует одну из комбинаций переменных х1х2 и в зависимости от нее включает в работу один из этих дешифраторов (рис. 8.7). Для работы DC1 на его вход Е необходимо подать постоянный сигнал, равный логической единице.

Таблица 8.3

Таблица истинности четырехразрядного дешифратора

Рис. 8.7. Четырехразрядный дешифратор, построенный на двухразрядных дешифраторах

Эту задачу можно решить и с использованием трехразрядных дешифраторов (рис. 8.8). При этом переменная х1 и ее инверсия включают или отключают дешифраторы DC1 или DC2.

Рис. 8.8. Четырехразрядный дешифратор, построенный на трехразрядных дешифраторах

| <== предыдущая страница | | | следующая страница ==> |

| Преобразование адреса с помощью автоформата при вводе | | | Шифраторы |

Дата добавления: 2014-10-10; просмотров: 1433; Нарушение авторских прав

Мы поможем в написании ваших работ!