Главная страница Случайная лекция

Мы поможем в написании ваших работ!

Порталы:

БиологияВойнаГеографияИнформатикаИскусствоИсторияКультураЛингвистикаМатематикаМедицинаОхрана трудаПолитикаПравоПсихологияРелигияТехникаФизикаФилософияЭкономика

Мы поможем в написании ваших работ!

Базис 2ИЛИ-НЕ

Реализация функционально полного набора функций 2И, 2ИЛИ, НЕ в базисе 2ИЛИ-НЕ:

4. Дизъюнктивные и конъюнктивные нормальные формы

Известно, что функция может быть задана в аналитическом виде (формулой) или в табличном виде. При этом, для того чтобы задать логическую функцию, не обязательно задавать все ее значения при всех сочетаниях переменных, а достаточно знать состояния, при которых она, например, равна единице (или нулю), так как для всех остальных состояний переменных значение функции равно нулю (единице).

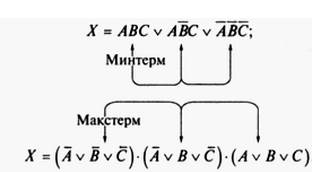

В виде формулы функция выглядит как набор логических произведений (или сумм) переменных, связанных между собой знаками логических сумм (или произведений), например:

Произведение переменных, в которое каждая из переменных входит только один раз в прямом или инверсном виде, называется минтермом, а сумма минтермов, образующих функцию, - дизъюнктивной нормальной формой (ДНФ).

Сумма переменных, в которую каждая из переменных входит только один раз в прямом или инверсном виде, называется макстермом, а произведение макстермов, образующих функцию, - конъюнктивной нормальной формой (КНФ).

5. Минимизация логических функций. Карты Карно/Вейча

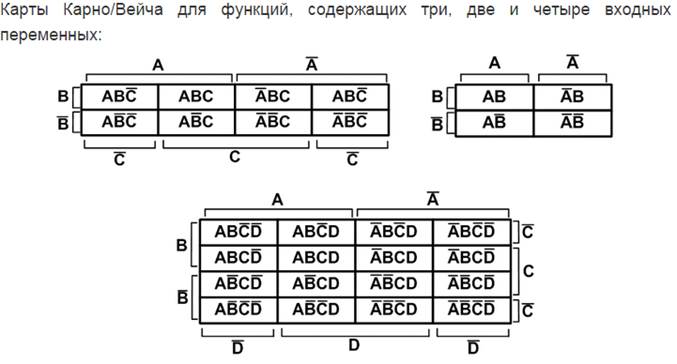

Для минимизации функций относительно небольшого числа переменной (не более шести) наиболее простым и наглядным является графический метод, использующий карты Карно.

Карта Карно – это прямоугольник, разбитый на квадраты, число которых равно числу наборов рассматриваемой функции, т. е. 2n. Клетки размечаются так, чтобы наборы, для которых возможны смежные конституенты, оказались бы в соседних клетках.

6. Условные графические обозначения логических схем. Цифровые микросхемы

7. Особенности работы комбинационных схем: гонки

Сигналы логической схемы могут в ней разветвляться, а затем снова сходиться. При прохождении сигналов через отдельные участки схемы время запаздывания в элементах схем может быть различным и определяется типом элементов на каждом участке, их количеством, быстродействием.

Такое соревновательное прохождение сигналов через различные участки логической схемы называется гонками.

Следующий простой пример демонстрирует, как из-за временной задержки сигнала в инверторе на выходе логической схемы формируется паразитный кратковременный импульс, которого в идеальном случае безинерционных элементов быть не должно.

Для борьбы с помехами, вызванными гонками, наиболее часто используется метод стробирования. В этом случае на логическую схему подается специальный сигнал -строб(сигнал разрешения на прохождение сигнала через схему), причем время поступления и длительность строба выбираются с учетом максимального запаздывания сигнала в участках схемы и меньше длительности самого сигнала.

Цифровые микросхемы по своим функциям делятся на два больших класса - комбинационные и последовательностные. К первому относятся микросхемы, не имеющие внутренней памяти (состояние выходов этих микросхем однозначно определяется уровнями входных сигналов в данный момент времени). Ко второму - микросхемы, состояние выходов которых определяется не только уровнями входных сигналов в данный момент времени, но и последовательностью состояний в предыдущие моменты времени из-за наличия внутренней памяти.

К комбинационным относятся простые логические микросхемы И-НЕ, И-ИЛИ-НЕ, НЕ, ИЛИ-НЕ, И, ИЛИ, более сложные элементы - дешифраторы, мультиплексоры, сумматоры по модулю 2, полные сумматоры, преобразователи кодов для семисегментных и матричных индикаторов, шифраторы, программируемые постоянные запоминающие устройства, преобразователи двоично-десятичного кода в двоичный и обратно, однонаправленные и двунаправленные буферные элементы, мажоритарные клапаны, триггеры Шмитта, которые, однако, имеют внутреннюю память и могут быть отнесены и к последовательностным микросхемам, а также некоторые другие.

К последовательностным микросхемам относятся триггеры, счетчики, сдвигающие регистры, оперативные запоминающие устройства и некоторые другие микросхемы.

Ждущие мультивибраторы нельзя отнести однозначно ни к одному из упомянутых классов, так как внутренняя память этих микросхем помнит изменение входных сигналов ограниченное время, после чего состояние выходов микросхемы ни от чего не зависит. То же самое относится и к генераторным микросхемам.

8. Анализ и синтез комбинационных схем

Комбинационные схемы состоят только из логических элементов (И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ и т.д.). Комбинационные схемы могут иметь несколько входов и несколько выходов.

Главной особенностью комбинационных схем является то, что сигнал на

выходе комбинационных схем зависит только от комбинации сигналов на

входах схемы и не зависит ни от времени, ни от предыстории входных

сигналов. Таким образом, при многократном поступлении одного и того же

входного сигнала на выходах комбинационной схемы будет формироваться

один и тот же входной сигнал.

В ходе разработки комбинационных схем приходится решать задачи анализа и синтеза.

Задача анализа состоит в определении статических и динамических свойств комбинационной схемы. В статике определяются логические функции, реализуемые комбинационной схемой по известной ей структуре. В динамике рассматривается способность надёжного функционирования схемы в переходных процессах при смене значений переменных на входах схемы, т.е. определяется наличие на выходах схемы возможных нежелательных импульсных сигналов, которые не следуют непосредственно из выражений для логических функций, реализуемых схемой.

Задача синтеза заключается в построении из заданного набора логических элементов комбинационной схемы, реализующей заданную систему логических функций.

Решение задачи синтеза не является однозначным, можно предложить различные варианты комбинационных схем, реализующих одну и ту же систему логических функций, но отличающихся по тем или иным параметрам. Разработчик комбинационных схем из этого множества вариантов выбирает один, исходя из дополнительных критериев: минимального количества логических элементов, необходимых для реализации схемы, максимального быстродействия и т.д. Существуют различные методы синтеза комбинационных схем, среди которых наиболее разработан канонический метод.

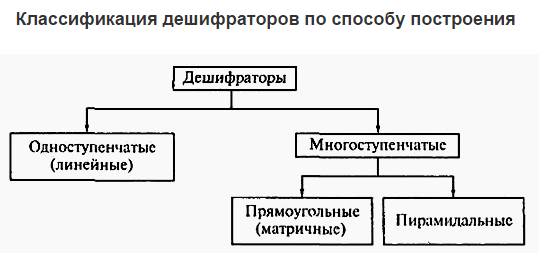

9. Комбинационные логические устройства: дешифраторы

Дешифратором называется комбинационная схема, преобразующая двоичный код, подаваемый на входы, в сигнал на одном из выходов, т.е. преобразуют двоичный код в унитарный код "1 из N". Полный дешифраторс n входами имеет 2n выходов, т.к. n-разрядный двоичный код может принимать 2n различных значений, и каждому из этих значений соответствует активный сигнал на соответствующем выходе дешифратора.Если в работе дешифратора используется неполное число выходов (меньшее 2n), то такой дешифратор называется неполным. Так, например, дешифратор, имеющий 4 входа и 24=16 выходов, будет полным, а если бы выходов было только 10, то он являлся бы неполным.

Одноступенчатые дешифраторы используются в тех случаях, когда количество разрядов дешифрируемого двоичного числа не превышает количества входов дешифратора.

В дешифраторах часто предусматривается операция стробирования, посредством которой выработка выходных сигналов разрешается только в момент подачи управляющего строба.

Области применения дешифраторов. Дешифраторы широко применяют в устройствах цифровой техники. Чаще всего они используются для формирования управляющих сигналов по определенному коду, в результате чего организуется доступ к другим элементам цифровых устройств.

10. Комбинационные логические устройства: шифраторы

Двоичные шифраторы выполняют операцию, обратную по отношению к операции дешифратора: они преобразуют унитарный код "1 из N" в двоичный. При активации одного i-го входа шифратора на его выходе формируется двоичный код числа i. Полный двоичный шифратор имеет N=2n входов и n выходов.

Функция шифратора обозначается буквами CD (coder). Входы шифратора нумеруются последовательными целыми числами 0, 1, ..., N-1, а метки выходов отображают веса двоичных разрядов выходного кода.

Приоритетные шифраторы выполняют более сложную операцию. При работе ЭВМ и других цифровых устройств очень часто возникает задача определения приоритетного претендента на пользование каким-либо ресурсом, когда несколько конкурентов выставляют запросы на обслуживание, которые не могут быть удовлетворены одновременно. Нужно выбрать запрос, которому предоставляется право первоочередного обслуживания.

Простейший вариант решения этой задачи - присвоение каждому источнику запросов фиксированного приоритета. Например, группа из 8 запросов R7...R0 (request - запрос) формируется так, что высший приоритет имеет запрос 7, а низший -запрос 0. Если одновременно имеется несколько запросов, то в первую очередь будет обслуживаться запрос с максимальным номером. Приоритетный шифратор вырабатывает на выходе двоичный код старшего запроса, т.е. при наличии на входах нескольких активных линий (запросов) на выходе будет возбуждена лишь одна, соответствующая старшему запросу.

Применения шифраторов. В цифровых устройствах шифраторы применяются для следующих операций: преобразования унитарного входного кода в выходной двоичный; ввода десятичных данных с клавиатуры в двоичном коде; выбор приоритетного запроса; указания старшей единицы в слове.

11. Комбинационные логические устройства: мультиплексоры

Мультиплексором называется функциональный узел, предназначенный для поочередной коммутации (переключения) информации от одного из n входов на общий выход. Номер конкретной входной линии, подключаемой к выходу определяется адресным кодом А1, А2, ... Связь между числом информационных n и адресных m входов определяется соотношением n = 2m. Таким образом, мультиплексор реализует управляемую передачу данных от нескольких входных линий на одну выходную.

Функция мультиплексоров записывается буквами MUX (multiplexor). Условное графическое обозначение мультиплексора показано на рисунке. Таблица истинности этого мультиплексора:

Мультиплексоры применяют для следующих операций: коммутации как отдельных, так и групп линий (шин); преобразования параллельного кода в последовательный; реализации логических функций; построения схем сравнения, генераторов кодов.

12. Комбинационные логические устройства: демультиплексоры

Демультиплексором называется функциональный узел, предназначенный для коммутации (переключения) сигнала с одного информационного входа D на один из n информационных выходов. Номер выхода, на который передается значение входного сигнала, определяется адресным кодом A1, A2, ... Адресные входы m и информационные выходы n связаны соотношением n = 2m или m = log2n.

Демультиплексор выполняет функцию, обратную функции мультиплексора. Применительно к мультиплексорам и демультиплексорам пользуются также термином "селекторы" данных. В условных графических обозначениях функция демультиплексора обозначается буквами DMX.

Работа двухадресного демультиплексора описывается логическими функциями:

Демультиплексоры используют для следующих операций: комммутации как отдельных линий, так и многоразрядных шин; преобразования последовательного кода в параллельный; реализации логических функций и др.

13. Комбинационные логические устройства: преобразователи кодов

Преобразователем кода называется функциональный узел, предназначенный для преобразования двоичного кода из одной формы в другую.

Для представления информации используют разнообразныеые двоичные и двоично-десятичные коды: прямой, обратный, дополнительный и их модификации и др. Существует множество кодов, которые обеспечивают:

- простоту выполнения арифметико-логических операций;

- удобство перевода чисел из десятичной системы в двоичный код;

- надежность выполнения заданных алгоритмов функционирования и эффективный контроль результатов вычислений;

- уменьшение аппаратных затрат при построении цифровых устройств.

Наиболее распространенными являются прямой, обратный и дополнительный коды.

К преобразователям кода относятся шифраторы и дешифраторы, однако по традиции эти функциональные узлы выделены в отдельные самостоятельные классы.

14. Комбинационные логические устройства: компараторы

Компараторы (устройства сравнения кодов) выполняют микрооперацию определения отношения между 2-мя словами. Основными отношениями можно считать "равно" и "больше". Другие отношения («меньше», «больше или равно» и т.д.) можно определить через основные, например, признак неравенства слов можно получить как отрицание (инверсию) признака равенства.

Отношения широко используются в микропрограммах как логические условия, а также в устройствах контроля и диагностики микропроцессорных систем (МПС).

15. Комбинационные логические устройства: полусумматор, полный сумматор, многоразрядный сумматор с последовательным и ускоренным переносом

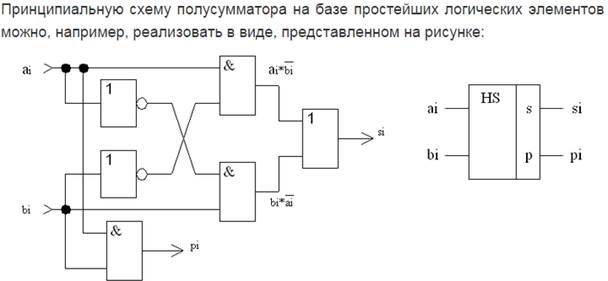

В цифровой вычислительной технике используются одноразрядные суммирующие схемы с двумя и тремя входами, причём первые называются полусумматорами, а вторые — полными одноразрядными сумматорами. Полусумматоры могут использоваться только для суммирования младших разрядов чисел. Полные одноразрядные сумматоры имеют дополнительный третий вход, на который подаётся перенос из предыдущего разряда при суммировании многоразрядных чисел.

Полусумматором называется комбинационная схема с двумя входами и двумя выходами, на которых вырабатываются сигнал суммы и переноса согласно правилам двоичной арифметики.

Правила двоичной арифметики при сложении двух одноразрядных двоичных чисел ai и bi имеют вид:

где si - сумма двух однобитовых чисел, pi - бит переноса в старший разряд.

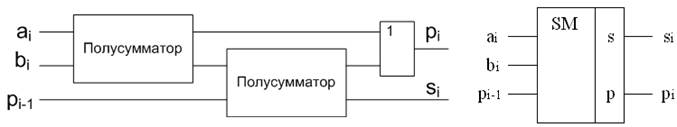

Полный сумматор можно представить как объединение двух полусумматоров:

На основе одноразрядных полных сумматоров и полусумматоров можно реализовать многоразрядные сумматоры с последовательным переносом, например:

Для повышения быстродействия сумматоров используют n-разрядные сумматоры с параллельными переносами. При этом сумматор разбивается на две части: собственно схему сложения и схему выработки ускоренных переносов (СУП).

16. Использование сумматоров для выполнения арифметических операций. Прямой, обратный и дополнительный коды

Основными арифметическими операциями являются сложение и вычитание. Разработаны коды дополнительный и обратный, которые позволяют выполнять операцию вычитания методом суммирования. Для выполнения операции вычитания, при использовании дополнительного кода, вычитаемое следует перевести в дополнительный код и просуммировать с первым слагаемым. Полученный результат (разность) будет представлен в дополнительном коде. Затем его следует перевести в прямой код.

Прямой и дополнительный код положительных чисел совпадают. При преобразовании отрицательного числа в дополнительный код все разряды прямого кода следует проинвертировать и к младшему разряду добавить единицу. При обратном преобразовании дополнительного кода в прямой результат следует также проинвертировать и к младшему разряду добавить единицу.

Таким образом, выполнение операции вычитания методом суммирования требует дополнительных затрат времени и снижает быстродействие вычислительных средств

17. Программируемые логические интегральные микросхемы

Программи́руемая логи́ческая интегра́льная схе́ма (ПЛИС, англ. programmable logic device, PLD) — электронный компонент, используемый для создания цифровых интегральных схем. В отличие от обычных цифровых микросхем, логика работы ПЛИС не определяется при изготовлении, а задаётся посредством программирования (проектирования). Для программирования используются программатор и IDE (отладочная среда), позволяющие задать желаемую структуру цифрового устройства в виде принципиальной электрической схемы или программы на специальных языках описания аппаратуры: Verilog, VHDL, AHDL и др. Альтернативой ПЛИС являются:

· программируемые логические контроллеры (ПЛК);

· базовые матричные кристаллы (БМК), требующие заводского производственного процесса для программирования;

· ASIC — специализированные заказные большие интегральные схемы (БИС), которые при мелкосерийном и единичном производстве существенно дороже;

· специализированные компьютеры, процессоры (например, цифровой сигнальный процессор) или микроконтроллеры, которые из‑за программного способа реализации алгоритмов в работе медленнее ПЛИС.

Некоторые производители для своих ПЛИС предлагают программные процессоры, которые можно модифицировать под конкретную задачу, а затем встроить в ПЛИС. Тем самым:

· обеспечивается увеличение свободного места на печатной плате (возможность уменьшения размеров платы);

· упрощается проектирование самой ПЛИС;

· увеличивается быстродействие ПЛИС.

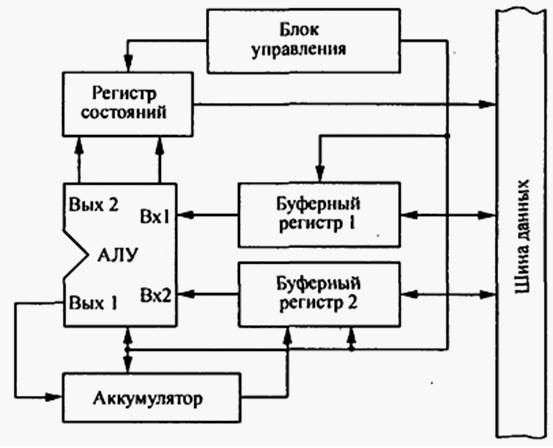

18. Принципы организации АЛУ

Арифметико-логическим устройством (АЛУ) называется функциональный узел ЭВМ, предназначенный для реализации логических и арифметических операций по обработке информации. Эти операции могут выполняться либо аппаратным способом - с использованием электронных устройств, либо программным способом - с применением последовательного исполнения нескольких операций, выполняемых аппаратным способом.

Выполняемые в АЛУ операции можно разделить на следующие группы:

- операции двоичной арифметики для чисел с фиксированной точкой;

- операции двоичной арифметики для чисел с плавающей точкой;

- операции десятичной арифметики;

- операции индексной арифметики (при модификации адресов команд);

- операции специальной арифметики;

-логические операции;

- операции над алфавитно-цифровыми полями.

19. Понятие цифрового конечного автомата. Последовательные цифровые устройства

Логические устройства разделяют на два класса: комбинационные и последовательностные.

Устройство называют комбинационным, если его выходные сигналы в некоторый момент времени однозначно определяются входными сигналами, имеющими место в этот момент времени.

Иначе устройство называют последовательностным, или конечным автоматом (цифровым автоматом, автоматом с памятью).

Понятие «автомат» происходит от греческого слова «αύτόματα», что означает «действующий самостоятельно». Теория автоматов тесно связана с теорией формальных языков и играет важную роль при создании компиляторов языков и анализаторов слов.

Автомат может находиться в одном из конечного числа состояний, отсюда название «конечный автомат»

Конечные автоматы представляют собой дискретные преобразователи информации, в которых содержится конечное множество входных и конечное выходных сигналов, а также конечное множество внутренних состояний.

Последовательностные цифровые устройства (ПЦУ) характеризуются тем, что выходные сигналы зависят не только от текущих значений входных сигналов, но и от последовательности значений входных сигналов, поступивших на входы в предшествующие моменты времени.

20. Общая структура и классификация триггеров

Триггер- это запоминающий элемент с двумя устойчивыми состояниями, изменение которых происходит под действием входных сигналов. Как элемент компьютера, триггер предназначен для хранения одного бита информации, то есть логического 0 или логической 1. Схема триггера обеспечивает запись, считывание, стирание и индикацию хранимой двоичной информации. На основе триггеров строят типовые функциональные узлы компьютеров - регистры, счетчики, накапливающие сумматоры, а также микропрограммные автоматы.

Все разновидности триггеров представляют собой элементарный автомат, включающий собственно элемент памяти (ЭП) и схему управления (СхУ), которая образует входную логику.

Состояние триггера определяется сигналами на прямом Q и инверсном ~Q выходах. При положительном кодировании информации высокий уровень напряжения на прямом выходе отображает значение логической 1 (состояние Q = 1), а низкий уровень - значение логический 0 (состояние Q = 0).

Входы триггераподразделяются на:

- информационные - R, S, J, К, D

- управляющие (вспомогательные) Т, V, С.

| <== предыдущая страница | | | следующая страница ==> |

| Логические функции двух переменных | | | Классификация триггеров |

Дата добавления: 2015-06-30; просмотров: 1279; Нарушение авторских прав

Мы поможем в написании ваших работ!