Главная страница Случайная лекция

Мы поможем в написании ваших работ!

Порталы:

БиологияВойнаГеографияИнформатикаИскусствоИсторияКультураЛингвистикаМатематикаМедицинаОхрана трудаПолитикаПравоПсихологияРелигияТехникаФизикаФилософияЭкономика

Мы поможем в написании ваших работ!

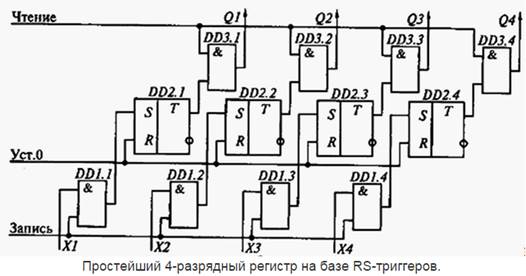

Классификация регистров

Регистры классифицируются по следующим видам:

- накопительные (регистры памяти, хранения);

- сдвигающие.

В свою очередь сдвигающие регистры делятся:

по способу ввода-вывода информации на:

- параллельные,

- последовательные,

- комбинированные;

по направлению передачи информациина:

- однонаправленные,

- реверсивные.

По способу приема и передачи информациирегистры подразделяются на:

- параллельные;

- последовательные;

- последовательно-параллельные.

25. Двоичные счетчики: классификация, параметры, схемы

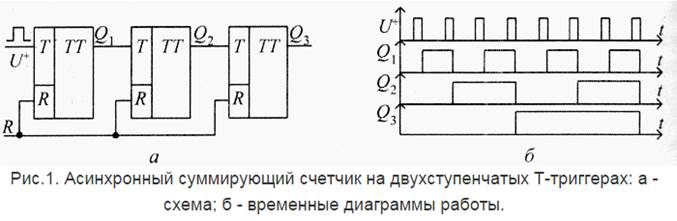

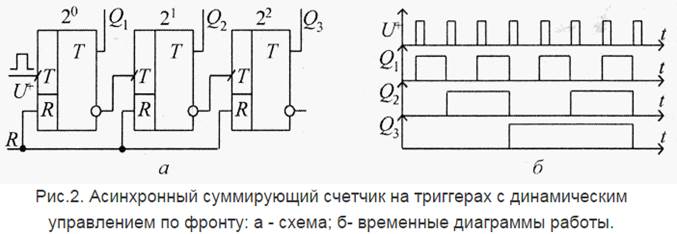

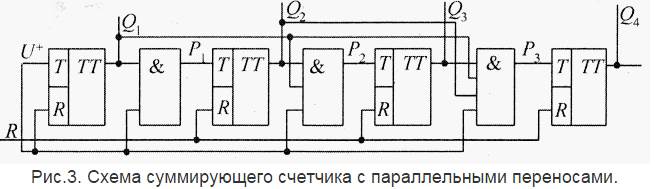

Счетчиком называется типовой функциональный узел, предназначенный для счета входных импульсов. Счетчик представляет собой связанную цепочку T-триггеров, образующих память с заданным числом устойчивых состояний.

Разрядность счетчика n равна числу T-триггеров. Каждый входной импульс изменяет состояние счетчика, которое сохраняется до поступления следующего сигнала.

Входные импульсы могут поступать на счетчик как периодически, так и произвольно распределенными во времени.

Счетчик является одним из основных функциональных узлов компьютера, а также различных цифровых управляющих и информационно-измерительных систем, главное применение счетчиков:

- образование последовательности адресов команд программы (счетчик команд или программный счетчик);

- подсчет числа циклов при выполнении операций деления, умножения, сдвига (счетчик циклов);

- получение сигналов микроопераций и синхронизации;

- аналого-цифровые преобразования;построение электронных таймеров (часов реального времени).

Счетчик характеризуется модулем и емкостью счета. Модуль счета Ксч определяет число состояний счетчика. Модуль двоичного n-разрядного счетчика выражается целой степенью двойки М = 2n;

Емкость счета определяет максимальное количество входных импульсов, которое может зафиксировать счетчик при одном цикле работы. Емкость счета равна Kсч-1 при условии, что работа счетчика начинается с нулевого начального состояния.

В счетчиках используются три режима работы: управления, накопления и деления.В режиме управления считывание информации производится после каждого входного счетного импульса, например, в счетчике адреса команд. В режиме накопления главным является подсчет заданного числа импульсов либо счет в течение определенного времени. В режиме деления(пересчета) основным является уменьшение частоты поступления импульсов в Kсч раз.

Большинство счетчиков может работать во всех режимах, однако в специальных счетчиках-делителях состояния в процecce счета могут изменяться в произвольном порядке, что позволяет упростить схему узла.

Счетчики классифицируют по следующим признакам:

- способу кодирования - позиционные и непозиционные;

- модулю счета - двоичные, десятичные, с произвольным постоянным или переменным (программируемым) модулем;

- направлению счета - простые (суммирующие, вычитающие) и реверсивные;

- способу организации межразрядных связей - с последовательным, сквозным, параллельным и комбинированным переносами (заемом);

- типу используемых триггеров - Т, JK, D в счетном режиме;

- элементному базису - потенциальные, импульсные и потенциал импульсные.

В вычитающих счетчиках каждый вычитаемый импульс уменьшает состояние на единицу, т.е. реализуется микрооперация декремента Сч:=Сч-1. После вычитания М импульсов счетчик выдает сигнал заема Z и возвращается в исходное (М-1)-е состояние.

Реверсивные счетчикимогут выполнять переходы в прямом и обратном направлениях, что позволяет считать как прибавляемые, так и вычитаемые импульсы.

К временным характеристикам счетчиков относятся разрешающая способность, быстродействие и время установления (переключения) кода.

Разрешающая способность tpc определяется минимальным интервалом времени между двумя входными импульсами, при котором еще сохраняется работоспособность счетчика.

Быстродействие счетчикаопределяется максимальной частотой Fm поступления входных импульсов в режиме деления и вычисляется по формуле Fm=1/tpc.

Время установления кода tyст отсчитывается от начала входного импульса до момента получения нового состояния.

26. Классификация и основные параметры микросхем памяти

Памятью МПС и компьютеров называется совокупность технических средств, предназначенных для приема, хранения и выдачи информации.

Основными операциями в памятив общем случае являются:

- занесение информации в память (запись);

- выборка информации из памяти (считывание);

- хранение информации в памяти.

Операции считывания/записи в памяти называются одним словом обращением к памяти.

Память характеризуется: информационной емкостью, физическим объемом, стоимостью, шириной выборки, потребляемой мощностью и быстродействием.

Основными характеристиками устройств памяти являются:

- информационная емкость, выражаемая количеством хранимой в памяти информации (в битах или байтах);

- быстродействие, определяемое временем выполнения операции записи или считывания данных. Производительность памяти можно также характеризовать скоростью потока записываемых или считываемых данных и измерять в бит/с (для внешних ЗУ с прямым или последовательным доступом).

Основными характеристиками устройств памяти являются:

- информационная емкость, выражаемая количеством хранимой в памяти информации (в битах или байтах);

- быстродействие, определяемое временем выполнения операции записи или считывания данных. Производительность памяти можно также характеризовать скоростью потока записываемых или считываемых данных и измерять в бит/с (для внешних ЗУ с прямым или последовательным доступом).

27. Общая характеристика запоминающих устройств. Иерархическая структура памяти в ЭВМ

Память современных МПС и компьютеров классифицируют по функциональному назначению, виду носителя информации, способу организации доступа к информации.

По функциональному назначению память компьютеров подразделяется на две основные группы: внешнюю и внутреннюю.

Внешние ЗУ предназначены для длительного хранения больших массивов информации с емкостью до гигабайта и более и малым быстродействием. Внешняя память включает в себя накопители на магнитных лентах, дисках, барабанах и оптических дисках.

Внутренние ЗУ предназначены для хранения программ и данных, обрабатываемых в текущий момент времени. К внутренней памяти относятся:

- сверхоперативные(регистровые) ЗУ, которые используют регистры общего назначения процессора; они обладают небольшой информационной емкостью и быстродействием работы процессора;

- кэш-память, которая служит для хранения копий информации, используемой в текущих операциях обмена. Высокое быстродействие кэш-памяти повышает производительность компьютера;

- оперативные, которые характеризуются высоким быстродействием и информационной емкостью до сотен мегабайт; оперативная память компьютеров первых поколений строилась на магнитных сердечниках. В настоящее время ОП реализуется на полупроводниковых БИС ЗУ. В процессе работы информация из внешней памяти при необходимости переписывается в оперативное ЗУ (ОЗУ);

- постоянные, которые строятся на полупроводниковых БИС. В постоянную память информация записывается заранее и ее можно только считывать. Оперативные и постоянные ЗУ образуют основную память компьютера;

- специализированные виды памяти - многопортовые, ассоциативные, видеопамять и др.

По физическому принципу построенияпамять компьютера бывает:

- магнитная (на сердечниках и пленках, на цилиндрических и плоских магнитных доменах);

- ультразвуковая (магнитострикционная, электрострикционная);

- сегнетоэлектрическая и голографическая (лазерная), на основе сверхпроводимости;

- полупроводниковая на БИС и СБИС, ультра-БИС.

Производительность и вычислительные возможности МПС и компьютеров в значительной степени определяются составом и характеристиками ее запоминающих устройств (ЗУ).

В составе МПС и компьютеров используется одновременно несколько типов ЗУ (типов памятей), отличающихся принципом действия, характеристиками и назначением.

28. Структура адресных запоминающих устройств

Основой любого ЗУ является элемент памяти (ЭП) статического или динамического типа, предназначенный для записи, хранения и считывания одного бита информации - цифры 0 или 1. Совокупность ЭП, которые образуют m-разрядное слово, называют ячейкой памяти (ЯП). Множество ЯП образуют запоминающий массив (ЗМ), называемый матрицей М элементов памяти.

Запоминающий элемент должен реализовывать следующие режимы работы:

- хранение состояния;

- выдача сигнала состояния (считывание);

- запись логического нуля;

- запись логической единицы.

К ЗЭ должны поступать управляющие сигналы для задания режима их работы, а также информационный сигнал при записи.

ЗМ имеет систему адресных и разрядных (информационных) линий.

Адресные линии используются для селекции по известному адресу совокупности ЗЭ, которым устанавливается режим записи или считывания.

Записываемая или считываемая информация передается по разрядным линиям.

Адресные и разрядные линии носят общее название линий выборки.

В зависимости от числа линий выборки, соединенных с одним ЗЭ, различают двух- и

3-координатные /трехмерные/ ЗУ, называемые ЗУ типа 2D, 3D и т.д. (от англ. Dimension - размерность).

29. ОЗУ статического типа (SRAM): особенности организации, применение в ПК

Статическая память с произвольным доступом (SRAM, static random access memory) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в динамической памяти (DRAM). Тем не менее, сохранять данные без перезаписи SRAM может только пока есть питание, то есть SRAM остается энергозависимым типом памяти.

Преимущества:

· Быстрый доступ. SRAM — это действительно память произвольного доступа, доступ к любой ячейке памяти в любой момент занимает одно и то же время.

· Простая схемотехника — SRAM не требуются сложные контроллеры.

· Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

Недостатки:

· Невысокая плотность записи (шесть-восемь элементов на бит, вместо двух у DRAM).

· Вследствие чего — дороговизна килобайта памяти.

SRAM применяется в микроконтроллерах и ПЛИС, в которых объём ОЗУ невелик (единицы килобайт), зато нужны низкое энергопотребление (за счёт отсутствия сложного контроллера динамической памяти), предсказываемое с точностью до такта время работы подпрограмм и отладка прямо на устройстве.

В устройствах с большим объёмом ОЗУ рабочая память выполняется как DRAM. SRAM же применяется для регистров и кеш-памяти.

30. ОЗУ динамического типа (DRAM): особенности организации, применение в ПК

DRAM (Dynamic random access memory, Динамическая память с произвольным доступом) — тип энергозависимой полупроводниковой памяти с произвольным доступом; DRAM широко используемая в качестве оперативной памяти современных компьютеров, а также в качестве постоянного хранилища информации в системах, требовательных к задержкам.

Физически DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, строку от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Основными характеристиками DRAM являются рабочая частота и тайминги.

При обращении к ячейке памяти контроллер памяти задаёт номер банка, номер страницы в нём, номер строки и номер столбца и на все эти запросы тратится время, помимо этого довольно большой период уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются: задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay), задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay), задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge). Тайминги измеряются в наносекундах или тактах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память.

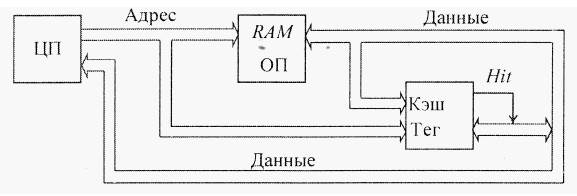

31. Назначение и принцип работы кэш-памяти

Кэш-память (от Cache — тайник) — это способ копирования и хранения блоко данных основной памяти типа DRAM в процессе выполнения программы. Кэш-память построена на быстродействующих триггерных ЭП, поэтому она имеет небольшую емкость в сравнении с основной динамической памятью. Кэш хранит ограниченное число данных и тегов. Тег содержит информацию о физическом адресе и состоянии данных.

При каждом обращении к основной памяти специальный контроллер проверяет по тегу наличие этой копии в кэше. Если она имеется, то вырабатывается сигнал Hit (кэш-попадание) и происходит обращение к кэш-памяти. Если копии нет (кэш-промах), то сигнал Hit не вырабатывается и выполняется чтение из ОП и одновременное размещение считанных данных в кэше.

Обмен с ОП может осуществляться двумя способами:

- обращение к ОП сочетается с одновременным поиском информации в теге. Обращение при попадании в ОП аннулируется;

- обращение к ОП осуществляется только после выявления кэш-промаха.

В современных компьютерах кэш строят по двухуровневой схеме:

- первичный кэш (L1 Cache) имеет объем десятки Кбайт и встраивается в процессор. Для повышения производительности часто используются раздельные кэши для команд и данных (Гарвардская архитектура);

- вторичный кэш (L2 Cache), обычно устанавливают на системной плате, он имеет объем несколько Мбайт.

Большинство прикладных программ имеет циклический характер и многократно использует одни и те же данные, поэтому наличие кэша уменьшает количество общений к относительно медленной ОП.

32. Паритетный контроль данных. Контроль по четности и нечетности

33. Общая структура микропроцессорной системы (МПС). Трехшинная организация МПС

Микропроцессор - центральная часть любой микропроцессорной системы (МПС) - включает в себя АЛУ и ЦУУ, реализующее командный цикл. МП может функционировать только в составе МПС, включающей в себя, кроме МП, память, устройства ввода/вывода, вспомогательные схемы (тактовый генератор, контроллеры прерываний и ПДП, шинные формирователи, регистры-защелки и др.).

В любой МПС можно выделить следующие основные части (подсистемы) :

- процессорный модуль;

- память;

- внешние устройства (внешние ЗУ + устройства ввода/вывода);

- подсистему прерываний;

- подсистему прямого доступа в память

Связь между процессором и другими устройствами МПС может осуществляться по принципам радиальных связей, общей шины или комбинированным способом. В однопроцессорных МПС, особенно 8- и 16-разрядных, наибольшее распространение получил принцип связи "Общая шина", при котором все устройства подключаются к интерфейсу одинаковым образом (Рис.1.1).

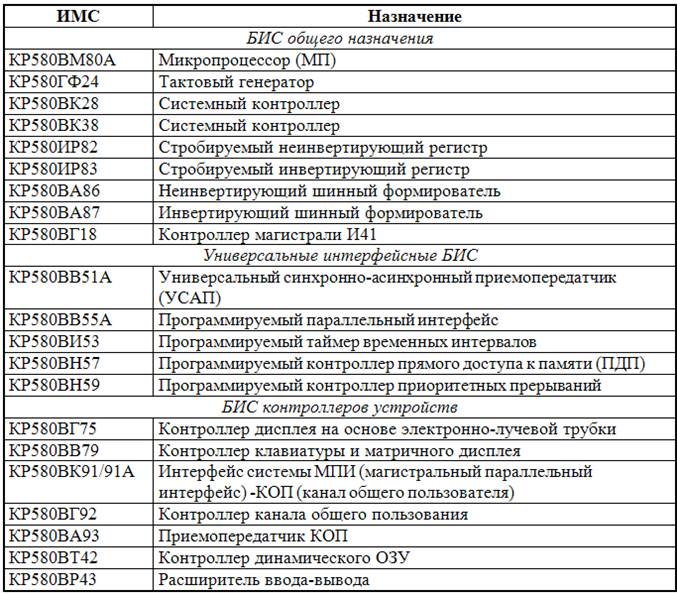

34. Микропроцессорный комплект КР580 и его назначение

Простейшую 8-разрядную микропроцессорную систему (МПС) можно построить на основе микропроцессорного комплекта (МПК) серии КР580.

МПК КР580 выполнен по n-МДП и ТТЛШ-технологиям. Он характеризуется архитектурным единством, обеспечиваемым автономностью и функциональной законченностью отдельных интегральных микросхем (ИМС), унификацией их интерфейса, программируемостью, их логической и электрической совместимостью.

МПК КР580 отличают:

- 8-разрядная организация;

- фиксированный набор команд;

- большой выбор периферийных больших интегральных схем (БИС) различного назначения;

- относительно высокое быстродействие;

- умеренное потребление мощности.

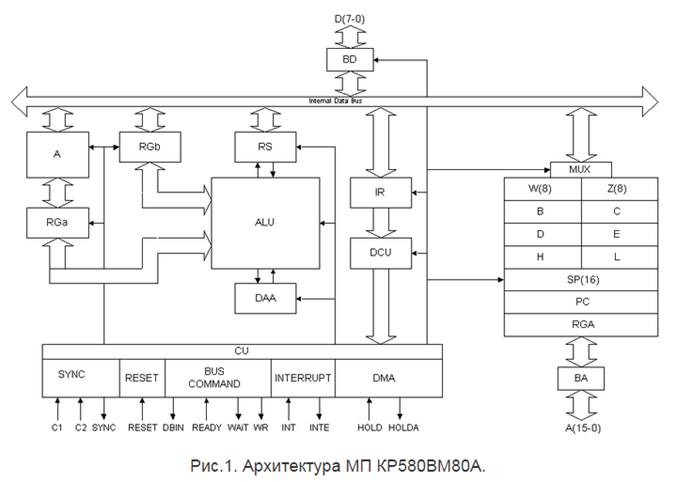

35. Архитектура микропроцессора КР580ВМ80А (i8080)

Структурная схема МП КР580ВМ80А приведена на рис.1.

В состав микропроцессора входят:

- 8-разрядное арифметико-логическое устройство АЛУ (ALU);

- регистр признаков RS, фиксирующий признаки, вырабатываемые АЛУ в процессе выполнения команды;

- аккумулятор (А);

- регистр аккумулятора (RGa);

- регистр временного хранения операндов (RGb);

- десятичный корректор (DAA), выполняющий перевод информации из двоичной в двоично-десятичную форму;

- регистр команд (IR), предназначенный для хранения первого байта команды, содержащего код операции;

- дешифратор команд (DCU);

- блок регистров для приема, выдачи и временного хранения информации в процессе выполнения программ;

- схема управления и синхронизации (CU), формирующая последовательности управляющих сигналов для работы ALU и регистров;

- однонаправленный 16-разрядный буферный регистр адреса (ВА);

- двунаправленный 8-разрядный буферный регистр данных (BD);

- двунаправленный мультиплексор (MUX) для обмена информацией между ALU и блоком регистров по внутренней шине данных (Internal Data Bus).

36. Работа микропроцессора КР580ВМ80А

С целью упрощения понимания принципа работы МП, дадим вначале словесное описание его функционирования во время выполнения команд программы:

1. Перед выполнением очередной команды МП содержит ее адрес в программном счетчике РС;

2. МП обращается к памяти по адресу, содержащемуся в РС, и считывает из памяти первый байт очередной команды в регистр команд IR;

3. Дешифратор команд DCU декодирует содержащийся в IR код команды и в результате его декодирования, в частности, "узнает":

- какова длина этой команды (1, 2 или 3 байта);

- где хранятся ее операнды;

- какие действия нужно выполнить над операндами;

4. В соответствии с полученной от DCU информацией устройство управления вырабатывает упорядоченную во времени последовательность микроопераций, реализующих предписания команды, в том числе:

- извлекает операнды из регистров и памяти;

- выполняет над ними предписанные кодом команды арифметические, логические или другие операции;

- в зависимости от длины команды модифицирует содержимое РС на 1, 2 или 3 (при линейном алгоритме);

- передает управление очередной команде, адрес которой снова находится в программном счетчике РС.

Рассмотрим, например, команду сложения содержимого аккумулятора и регистра В, имеющую мнемоническое обозначение ADD B. Команда ADD B - однобайтовая и имеет код операции 80h.

В начале выполнения этой команды МП выставляет на шину адреса адрес команды, считывает из памяти ее код 80h и помещает его в регистр команд IR. После декодирования команды устройство управления (УУ) вырабатывает предписанную командой последовательность управляющих сигналов, приводящую к следующим действиям:

- содержимое аккумулятора копируется в RGa;

- содержимое регистра В копируется RGb;

- производится суммирование RGa+RGb и результат сложения помещается в аккумулятор А;

- в зависимости от результата операции модифицируется содержимое регистра флагов RS;

- содержимое программного счетчика РС увеличивается на 1, так как команда ADD B является однобайтовой, и теперь программный счетчик содержит адрес следующей команды программы и т.д.

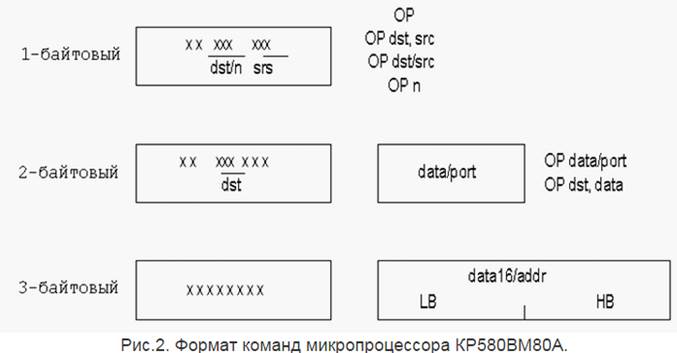

37. Формат данных и система команд микропроцессора КР580ВМ80А

Всего в систему команд ВМ80А входят 78 базовых команд, содержащих 111 кодовых операций. В зависимости от своего назначения команда может иметь длину в один, два или три байта и соответственно занимает в памяти от одной до трех последовательных ячеек. Программный счетчик РС микропроцессора всегда содержит адрес первого байта команды, которая будет выполняться вслед за командой, которая выполняется в текущий момент времени.

В МП ВМ80А применяется довольно простой формат команд (рис. 2):

Система команд МП состоит из 5 групп:

команды пересылки (14 команд, 28 операций);

логические команды ( 15 команд, 19 операций);

арифметические команды (14 команд, 29 операций);

команды передачи управления (28 команд, 28 операций);

команды управления процессором (7 команд, 7 операций).

38. Синхронизация микропроцессора КР580ВМ80А. Типы машинных циклов

Все действия МП синхронизованы вложенными друг в друга циклами трех уровней: командными, машинными и микротактами.

Командный цикл состоит из 1..5 машинных циклов обозначаемых М1..М5. Каждыймашинный цикл представляет собой цикл обращения к системной магистрали: выборка команды, выборка операнда; их запись; ввод-вывод данных. Исключением являются две команды: команда DAD, содержащая 3 машинных цикла, из которых только в цикле М1 происходит обращение к памяти, и команда HLT. Цикл М1 всегда реализует выборку кода команды (цикл FETCH).

Машинные циклы выполняются по микротактам, определяемым как интервал времени между двумя соседними фронтами синхроимпульсов фазы С1. Любой МЦ включает, по крайней мере, три такта (Т1-Т3). Такты Т4 и Т5 необязательны и применяются в отдельных командах для внутренних операций МП.

Сигнал SYNC выдается в первом микротакте каждого МЦ и служит признаком того, что по шине данных микропроцессор выдает слово состояния (SW), которое кодирует тип выполняемого МЦ. Это слово должно фиксироваться во внешнем регистре по условию SYNC*C1=1 и сохраняться в нем на протяжении всего МЦ. Слово состояния SW содержит дополнительную информацию о выполняемом цикле обращения к магистрали.

В состав SW входят следующие сигналы:

- INTA - подтверждение прерывания. Выделяет МЦ обслуживания системы прерываний;

- WO - запись/вывод. Свидетельствует о выдаче в данном цикле данных из МП;

- STACK - обращение к стеку. Стек активен, если выполняется обращение к нему, т.е. addr=(SP);

- HLTA - подтверждение останова. Информирует о переходе МП в данном машинном цикле в состояние останова HALT.

- OUT - вывод. Свидетельствует об обращении к портам вывода. Для повышения нагрузочной способности шины адреса микропроцессора один и тот же адрес порта устанавливается на младшей и старшей половинах шины адреса одновременно;

- М1 - цикл М1. Обозначает первый МЦ каждого КЦ.

- INP - ввод. Свидетельствует об обращении к портам ввода (об адресе см. OUT);

- MEMR - чтение памяти. Выделяет циклы чтения данных из памяти.

Всего возможно 11 различных наборов сигналов SW, т.е. возможно 11 типов машинных циклов:

- FETCH - цикл М1 выборки кода команды в регистр команд IR;

- MEMORY_READ - чтение данных из памяти по адресу, определяемому содержимым регистров PC, BC, DE, HL или значением addr 16;

- MEMORY_WRITE - запись данных в память по адресу, определяемому содержимым регистров PC, BC, DE, HL или значением addr 16;

- STACK-READ - цикл чтения из стека;

- STACK_WRITE - цикл записи в стек;

- 6) INPUT - ввод данных из порта в аккумулятор;

- OUTPUT - вывод данных из аккумулятора в порт;

- INTERRUPT_M1 - первый цикл подтверждения прерывания (ППР);

- HALT - цикл останова МП;

- HALT - INTERRUPT - первый цикл ППР в состоянии HALT;

- INTERRUPT - второй и третий циклы ППР.

39. Микропроцессорный комплект К1810 и его назначение

Успешное решение многообразных задач с помощью микропроцессорных средств требует постоянного улучшения характеристик последних, прежде всего производительности, и расширения функциональных возможностей. Этим требованиям на современном этапе отвечает поколение микропроцессорных комплектов (МПК). БИС повышенных степени интеграции, разрядности и быстродействия. Типичным представителем этого поколения является МПК БИС серии К1810.

40. Архитектура и работа микропроцессора К1810ВМ86 (i8086)

К1810ВМ86 — советский однокристальный 16-разрядный микропроцессор, выполняющий около 2 млн операций в секунду. Синхронизируется тактовой частотой от 2 до 5 МГц. Является клоном микропроцессора Intel 8086 с тактовой частотой до 10 МГц.

Входит в состав микропроцессорного комплекта серии КР1810, предназначенного для построения микро-ЭВМ.

Имеет 20-ти разрядную шину адреса, что позволяет обеспечить прямую адресацию 1 Мбайт внешней памяти. Область адресного пространства памяти разбита на сегменты по 64 КБ. Такая организация памяти обеспечивает удобный механизм вычисления физических адресов. Шина адреса и шина данных мультиплексированы. При организации вычислительных систем их нужно разделить (регистры-защелки). Микропроцессор может обращаться как к памяти, так и ко внешним устройствам.

При обращении ко внешним устройствам используются 16 младших линий шины адреса. Следовательно, можно подключить 64 К 8-битных внешних устройств либо 32 К 16-ти разрядных. Микропроцессор имеет многоуровневую систему прерываний: 256 векторов прерываний.

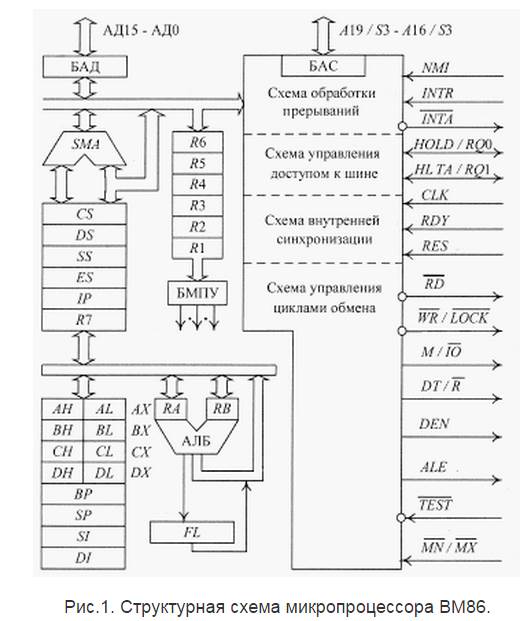

Структурная схема МП К1810ВМ86 приведена на рис.1.

ВМ86 содержит две относительно независимые части:

- операционное устройство (ОУ), реализующее команды;

- устройство шинного интерфейса (ШИ), осуществляющее выборку команд из памяти, обращения к памяти и ВУ для считывания операндов и записи результатов.

Оба устройства могут работать параллельно, обеспечивая совмещение во времени процессов выборки и исполнения команд, что повышает быстродействие МП.

41. Формат данных и система команд микропроцессора К1810ВМ86

МП ВМ86 относится к классу однокристальных с фиксированной системой команд. Команды МП ВМ86 могут адресовать один или два операнда, причем 2-операндные команды являются, как правило, симметричными, то есть результат операции можно направить на место любого из операндов. Один из двух операндов должен обязательно располагаться в регистре, так как имеются команды типа регистр-регистр, но отсутствуют команды типа память-память (за исключением команды пересылки цепочки байт).

Система команд ВМ86 содержит 91 мнемокод и позволяет совершать операции над байтами, двухбайтовыми словами, отдельными битами, а также цепочками байтов и слов. Имеется широкий набор арифметических команд, включающий умножение и деление, который ориентирован на обработку как беззнаковых, так и знаковых чисел. Весьма разнообразны команды пересылки данных, логических операций, переходов в программе и вызовов подпрограмм, а также управления микропроцессором. Число вариантов команд, т. е. число различных машинных кодов, превышает 3800 благодаря использованию восьми способов адресации в их различных модификациях. Тем самым обеспечивается гибкость применения большого числа команд, что позволяет выбрать наиболее рациональные способы адресации в конкретных случаях. Это особенно важно при обработке сложных структур данных.

По функциональному признаку система команд ВМ86 разбивается на шесть групп: пересылка данных, арифметические операции, логические операции и сдвиги, передача управления, обработка цепочек и управление микропроцессором.

42. Адресное пространство памяти и ввода-вывода микропроцессора К1810ВМ86. Сегментация памяти

| <== предыдущая страница | | | следующая страница ==> |

| Классификация триггеров | | | Адресное пространство памяти и ввода-вывода |

Дата добавления: 2015-06-30; просмотров: 1032; Нарушение авторских прав

Мы поможем в написании ваших работ!