Главная страница Случайная лекция

Мы поможем в написании ваших работ!

Порталы:

БиологияВойнаГеографияИнформатикаИскусствоИсторияКультураЛингвистикаМатематикаМедицинаОхрана трудаПолитикаПравоПсихологияРелигияТехникаФизикаФилософияЭкономика

Мы поможем в написании ваших работ!

Исключительные ситуации

Исключительные ситуации, генерируемые микропроцессором, возникают в процессе и по результатам выполнения команд. Исключительные ситуации условно разделены на три типа в зависимости от того, чем они были вызваны и поддерживается ли рестарт вызвавшей их команды.

Ошибки представляют собой исключительные ситуации, которые обнаруживаются и обслуживаются после выборки до выполнения ошибочной команды. Чаще всего при возникновении ошибки возможен рестарт данной команды. Пример ошибки: обращение по адресу, находящемуся в отсутствующей в оперативной памяти странице.

Ловушки представляют собой исключительные ситуации, о которых сообщается сразу после выполнения команды, послужившей причиной возникновения данной исключительной ситуации.

Аварийные завершения - исключительные ситуации, которые возникают при невозможности точно обнаружить источник ошибки и используются при обнаружении крупных ошибок и технических неисправностей. Технические прерывания (или прерывания от схем контроля) возникают при появлении отказов и сбоев в работе технических средств микроЭВМ. Большинство технических прерываний не маскируется, т.е. они разрешаются всегда. При их возникновении даже не запрашивается причина прерывания, а, по-возможности, спасаются важные промежуточные результаты – записываются в безопасное место, на винчестер, например.

При появлении запроса на прерывание микропроцессор, после завершения выполнения текущей команды программы, анализирует допустимость (разрешенность и приоритетность) данного вида прерывания. Если прерывание разрешено, микропроцессор выполняет следующие действия: 1) запоминание в стековой памяти текущего состояния регистров микропроцессора, 2) выполнение подпрограммы обработки прерывания, 3) восстановление состояния регистров микропроцессора и возврат к выполнению прерванной программы.

- Отличительные особенности архитектуры 32-разрядного МП.

Микропроцессор 80486 появился в 1989 году. Микропроцессор 80486 реализован с использованием CISC архитектуры и обеспечивает программную совместимость с младшими моделями микропроцессоров типа 80Х86. Все 32-разрядные процессоры могут работать в двух режимах: реальном и защищенном. Основные архитектурные особенности микропроцессора 80486:

1. в архитектуре применено RISC-ядро, позволяющее наиболее часто встречающиеся инструкции выполнять за 1 такт;

2. наличие встроенного арифметического сопроцессора;

3. наличие внутренней кэш-памяти и предусмотрены все необходимые средства для построения памяти с двухуровневым кэшированием;

4. увеличена очередь команд до 16 байт;

5. ускорено выполнение операций как в целочисленном АЛУ, так и в блоке арифметического сопроцессора;

6. используется умножение тактовой частоты системной платы (с увеличенной частотой работают только внутренние схемы микропроцессора, все внешние по отношению к микропроцессору схемы, в том числе расположенные и на системной плате, работают с обычной частотой).

Концепция RISC-микропроцессора сводится к следующим положениям:

· выполнение всех (или, по крайней мере, 75% команд) за один цикл;

· стандартная длина всех команд;

· малое число команд;

· малое количество форматов команд;

· малое число способов адресации (преимущественно регистровая и непосредственная);

· все команды, за исключением «Чтения» и «Записи», используют внутрипроцессорные межрегистровые пересылки;

· относительно большой процессорный файл РОН.

- Общие сведения о режимах работы 32-разрядного МП.

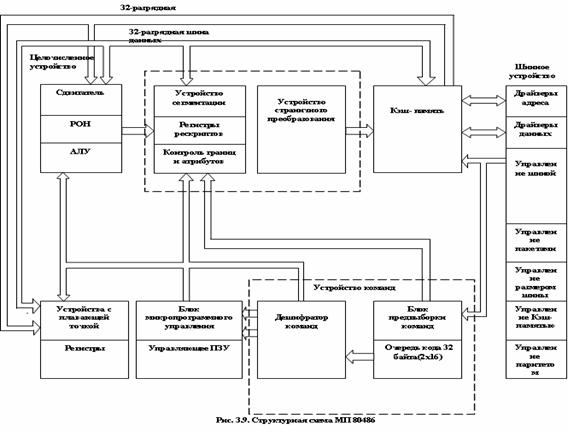

- Обобщенная структурная схема 32-разрядного МП.

В состав структурной схемы микропроцессора 80486 входят

1. целочисленное устройство,

2. устройство с плавающей точкой,

3. устройство управления,

4. диспетчер памяти,

5. устройство команд,

6. кэш-память,

7. шинное устройство.

В состав целочисленного устройства входят АЛУ, 8 32-разрядных РОН и многоразрядный сдвигатель, используемый при арифметических и циклических сдвигах, операциях умножения и деления. Команды сложения, вычитания, сдвига и логические операции выполняются за один такт. Содержимое РОН используется устройством сегментации для формирования адресов.

Устройство с плавающей точкой по структуре и программному обеспечению соответствует математическому сопроцессору.

Целочисленное устройство и устройство с плавающей точкой соединены двумя 32-разрядными двунаправленными шинами, которые применяются совместно для пересылки 64-разрядных операндов, а также для связи с кэш-памятью.

Диспетчер памяти состоит из устройства сегментации и страничного преобразования и обеспечивает двухступенчатое формирование физического адреса ячейки памяти сначала в пределах сегмента, а затем в пределах страницы. Диспетчер поддерживает реальный и защищенный режимы работы микропроцессора. В реальном режиме микропроцессор 80486 работает как очень быстрый микропроцессор 8086. При этом реализуется расширенный набор команд, допускается увеличение разрядности операндов и адресов до 32. В реальном режиме возможна адресация до 1 Мбайт физической памяти. В защищенном режиме допустимо выполнение нескольких задач (программ). Задачи в этом случае изолированы и защищены одна от другой. Механизмы защиты контролируют попытки выполнения недопустимых команд, выход за рамки отведенного пространства памяти и разрешенной области ввода-вывода. В защищенном режиме микропроцессор позволяет адресовать до 4 Гбайт физической памяти. Сегментация обеспечивает мобильность и защищенность программ. Каждый сегмент разделяется на страницы размером по 4 Кбайт, которые могут размещаться в любом месте памяти. Устройство страничной адресации действует только в защищенном режиме.

Дополнением режимов является режим виртуальной адресации или виртуальный режим. Этот режим является особым состоянием защищенного режима, в котором микропроцессор функционирует как 8086, однако может адресовать до 4 Мбайт физической памяти.

Шинное устройство поддерживает обмен микропроцессора с памятью, контроллерами ввода-вывода и другими активными внешними устройствами. Оно содержит драйверы шины адреса и данных, схемы управления размером шины данных, шиной, пакетами, кэш-памятью, паритетом.

Шинное устройство осуществляет обмен посредством 32-разрядной двунаправленной шины данных, 34-разрядной шины адреса и 32-разрядной шины управления.

Разрядность шины данных микропроцессора 80486 может изменяться таким образом, что за один цикл осуществляется передача 8, 16 или32 разрядов. Шина адреса включает 30 адресных линий и четыре линии выбора байтов. Посредством сигналов выбора байтов реализуется выбор байтов 32-разрядной шины данных для текущего цикла обмена, что позволяет без дополнительного оборудования согласовать 32-разрядную шину данных микропроцессора с байтовой организацией памяти.

Схемы управления имеют два типа выводов:

1. сигналы управления циклами магистрали,

2. сигналы управления состоянием микропроцессора и взаимодействием микропроцессора с другими активными устройствами магистрали.

К основным отличиям в работе шинного устройства микропроцессора 80486 относятся:

§ машинный такт длительностью в один период внешнего синхросигнала,

§ возможность пакетной передачи для пересылки длинных операндов (при считывании максимальная длина пакета составляет 128 бит, а при записи – 32 бита),

§ управление паритетом. Каждый байт шины данных имеет бит паритета. Контроль четности (количество единиц в байте вместе с битом паритета должно быть четным) выполняется для всех байт, участвующих в конкретном цикле обмена.

Микропроцессор 80486 имеет внутреннюю кэш-память, единую для команд и данных. Кэш-память представляет собой быстродействующую память ограниченного объема, в которой хранятся копии последних считанных команд и операндов. Когда микропроцессор обращается за командой или данными, то сначала производится поиск требуемой информации в кэш-памяти. При отсутствии необходимой информации в кэш-памяти производится обращение к оперативной памяти и одновременная запись в кэш-память. При записи соответствие содержимого оперативной и кэш-памяти достигается с помощью механизмов сквозной записи. При сквозной записи осуществляется одновременное изменение содержимого как кэш-памяти, так и оперативной памяти.

Устройство команд содержит блок предвыборки для создания очереди команд, готовых к выполнению, и дешифратор команд. Блок предвыборки позволяет с опережением получить команды из памяти перед их фактическим исполнением. Дешифратор команд получает команды от блока предвыборки и преобразует их в управляющие сигналы. В дешифраторе одновременно обрабатываются коды операций, байты адресации и смещения. Выходные сигналы дешифратора определяют аппаратные микрокоманды для устройства сегментации, целочисленного устройства и устройства с плавающей точкой.

Блок микропрограммного управления формирует управляющие микропрограммы.

- Регистровая структура 32-разрядного МП.

- Регистр флагов 32-разрядного МП.

- Регистры пользователя 32-разрядного МП.

Программная модель 32-разрядного микропроцессора содержит следующие группы регистров:

- регистры пользователя,

- системные регистры (используются разработчиками операционной системы).

Группа регистров пользователя включает:

1) РОН - используются для хранения операндов и результатов выполнения команд, а также для формирования адреса при обращении к данным в памяти

| |||

| |||

| |||

| |||

2) указатель команд содержит смещение команды в пределах сегмента команд

| |||

| |||

3) регистр флагов отражает текущее состояние микропроцессора, а также служит для задания режима работы микропроцессора, управления вводом-выводом, маскируемыми прерываниями, отладкой, переключением задач. Младшие 16 разрядов регистра флагов представляют собой 16-разрядный регистр флагов 16-разрядного микропроцессора 8086.

| |||

| |||

В регистр флагов микропроцессора 80486 добавлены новые флаги:

AC – установка флага включает контроль выравнивания при обращении к памяти. При этом генерируется сигнал прерывания, если используется невыровненный операнд, например слово по нечетному адресу или двойное слово по адресу, не кратному четырем.

При размещении информации в памяти придерживаются принципа целочисленных границ. Согласно этому принципу, начальный адрес слова принимается кратным двум, а двойного слова – четырем. Так как ширина выборки из памяти (т.е. число байт, которые считываются/ записываются за одно обращение), как правило 2 или 4 байта, то слово или двойное слово, размещенное в памяти по целочисленным границам, будет читаться/ записываться за минимальное число обращений к памяти.

VM – флаг переключения микропроцессора в виртуальный режим.

RF – флаг возобновления. В режиме отладки при RF=1 осуществляется рестарт команды после прерывания. RF автоматически сбрасывается при успешном завершении команды.

NT – признак вложенности задачи, используется микропроцессором в защищенном режиме для управления последовательностью прерываемых и вызываемых задач. NT устанавливается для указания, что данная задача выполняется будучи вложенной в другую задачу.

IOPL – уровень привилегий ввода-вывода. Биты IOPL показывают максимальную величину уровня привилегий ввода-вывода для текущей задачи, при котором разрешено выполнение команд ввода-вывода. IOPL используется механизмами защиты для управления доступом к адресному пространству ввода-вывода.

4) сегментные регистры применяются при формировании полного логического адреса. В защищенном режиме работы микропроцессора сегментные регистры называются селекторными или просто селекторами

|

Группа системных регистров включает:

1) регистры управления управляют функционированием микропроцессора (управление режимами работы кэш-памяти, режимами работы устройства с плавающей точкой),

2) системные адресные регистры используются для хранения базовых адресов дескрипторных таблиц,

3) регистры отладки предназначены для проверки и отладки программы. Эти регистры позволяют устанавливать контрольные точки для обнаружения мест возникновения ошибок,

4) регистры тестирования служат для проверки внутренней кэш-памяти.

| <== предыдущая страница | | | следующая страница ==> |

| Программные прерывания | | | Типы данных 32-разрядных МП |

Дата добавления: 2014-08-04; просмотров: 515; Нарушение авторских прав

Мы поможем в написании ваших работ!