Главная страница Случайная лекция

Мы поможем в написании ваших работ!

Порталы:

БиологияВойнаГеографияИнформатикаИскусствоИсторияКультураЛингвистикаМатематикаМедицинаОхрана трудаПолитикаПравоПсихологияРелигияТехникаФизикаФилософияЭкономика

Мы поможем в написании ваших работ!

Кодирующие устройства с линейной шкалой квантования

Кодирующее устройство (кодер) предназначено для преобразования отсчетов напряжений U в эквивалентную кодовую комбинацию (или число N).

В зависимости от вида функции преобразования кодеры классифицируются:

- на кодеры с линейной шкалой квантования;

- на кодеры с нелинейной шкалой квантования.

По принципу действия различают следующие виды кодеров:

- кодеры последовательного счета;

- кодеры с поразрядным взвешиванием;

- матричные кодеры.

Рассмотрим работу некоторых видов кодеров.

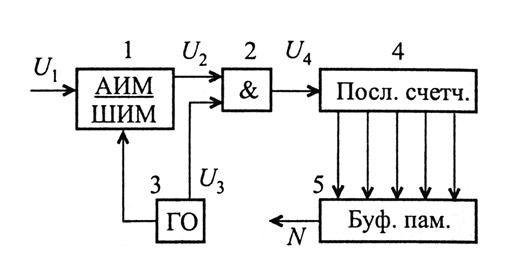

Линейный кодер последовательного счета строится по схеме изображенной на рисунке 40, где блоки: 1 – широтно-импульсный модулятор; 2 – схема И; 3 – генератор импульсов; 4 – последовательный счетчик импульсов; 5 – буферная память.

Рисунок 40 Структурная схема линейного кодера

последовательного счета

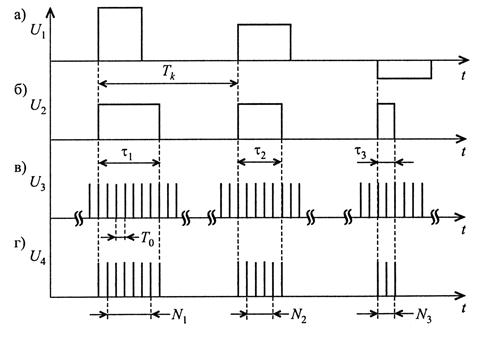

Входной АИМ сигнал U1 (рисунок 41,а) преобразуется в широтно-импульсно-модулированный (ШИМ) сигнал U2. Длительность импульсов ШИМ сигнала  i пропорциональна амплитуде импульсов входного АИМ сигнала (рисунок 41,б). Модулированные по длительности импульсы подаются на первый вход логической ячейки И, на второй вход которой подается

i пропорциональна амплитуде импульсов входного АИМ сигнала (рисунок 41,б). Модулированные по длительности импульсы подаются на первый вход логической ячейки И, на второй вход которой подается

Рисунок 41 – График поясняющий работу линейного кодера последовательного счета

последовательность коротких импульсов U3 (рисунок 41,в) от генераторного оборудования. На выходе ячейки И получим пачки импульсов U4 (рисунок 41,г); количество импульсов в каждой пачке Ni пропорционально длительности импульсов ШИМ и, следовательно, пропорционально амплитуде импульсов (отсчетов) АИМ сигнала U1. Далее сигнал U4 поступает на последовательный счетчик, который выполнен на триггерах Т1 ÷ Тт ( т - количество разрядов в кодовой группе параллельного кода). По окончании процесса счета производится сброс ячеек счетчика (опустошение) в буферную память, на выходе которой получаем ИКМ сигнал в последовательном коде.

Достоинством кодера линейного счета является простота, надежность и повышенная точность работы.

К недостаткам схемы можно отнести необходимость использования логических элементов с высоким быстродействием.

Линейные кодеры взвешивающего типа имеют несколько вариантов построения.

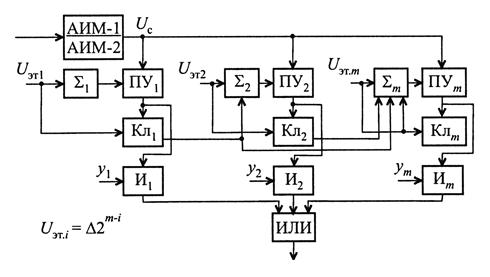

Рисунок 42 – Структурная схема кодера взвешивающего типа параллельного действия

На рисунке 42 представлена структурная схема линейного кодера взвешивающего типа параллельного действия. Схема содержит:

- блок преобразования дискретных отсчетов АИМ-1/АИМ-2;

- пороговые устройства (схемы сравнения) ПУ1 ÷ ПУт;

- сумматоры ∑1 ÷ ∑т ;

- аналоговые ключи Кл1 ÷ Клт ;

- схемы совпадения И1 ÷ Ит ;

- источники эталонных напряжений Uэт.1 ÷ Uэт.т ;

- схему логического сложения ИЛИ ("1"),

где т – число разрядов двоичного числа N на выходе кодера.

В блоке преобразования дискретных отсчетов происходит преобразование сигнала АИМ-1 в АИМ-2, который поступает на входы всех схем сравнения. На вход i -й схемы сравнения (i  [1… т]) через i -й сумматор поступает эталонное напряжение Uэт..i =

[1… т]) через i -й сумматор поступает эталонное напряжение Uэт..i =  · 2 m –i , где i – номер текущего эталона.

· 2 m –i , где i – номер текущего эталона.

Операция взвешивания осуществляется в т этапов.

Сигнал Uс сравнивается с эталонным значением Uэт.1, и если Uс < Uэт.1, то ключ Кл1 будет закрыт, и на вход схемы И1 поступит сигнал "0". В этом случае Uс, поступающее на ПУ2 , сравнивается только с эталонным значением Uэт.2 .

Если Uс > Uэт.2 , то срабатывает ключ Кл2 , и одновременно сигнал разрешения проходит на вход логической ячейки И2 . С приходом импульса опроса y2 эта схема открывается, и на вход схемы ИЛИ поступит сигнал "1" во 2-м разряде числа N.

Далее Uс поступает на ПУ3 , где уже сравнивается сумма эталонных значений Uэт.2 + Uэт.3 с информационным сигналом (Uс). При Uс > (Uэт.2 + Uэт.3) срабатывает ключ Кл3, и на вход схемы И3 поступает сигнал "1".

Таким образом, с выхода схемы ИЛИ получаем 3-х разрядную кодовую группу (число N) – "011", если бы рассматривалась работа трехрзрядного кодера (т = 3).

Практически процедура взвешивания (включение соответствующих эталонных напряжений) выполняется очень быстро, за время меньшее, чем тактовый период (Тт). Остальное время уходит на преобразование числа N из параллельного кода в последовательный по состояниям напряжений на входах И1 ÷ Ит.

К достоинствам такого кодера можно отнести высокую точность и высокую скорость кодирования, к недостаткам – сложность построения кодера.

Простотой построения отличается кодер с декодером в цепи обратной связи (ОС) или кодера последовательного действия.

Взвешивающий кодер такого типа можно построить на одной схеме сравнения (пороговом устройстве), когда кодовые символы будут формироваться последовательно с помощью цепи ОС, содержащей декодер.

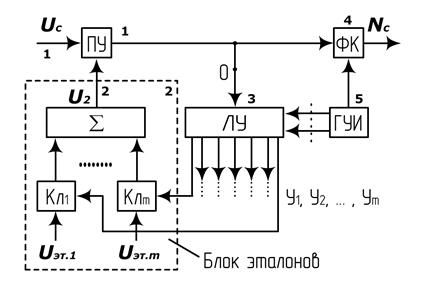

Структурная схема такого кодера представлена на рис.33. Декодер образуют логика управления (ЛУ) и блок эталонов, содержащий ключи

Кл1 ÷ Клт и аналоговый сумматор напряжений ∑.

Рисунок 43 – Структурная схема кодера последовательного действия

На вход 1 ПУ (схемы сравнения) подается выборка сигнала, которая с помощью модулятора АИМ-2 запоминается на период кодовой комбинации. Схема сравнения вырабатывает двоичное решение: сигнал на входе 1 больше или меньше, чем на входе 2. В простейшем случае схема сравнения может быть построена в виде дифференциального усилителя, работающего в режиме ограничения. На вход 2 схемы сравнения поступает эталонный сигнал U2, вырабатываемый блоком эталонов 2. Работой этого блока управляет логика 3, алгоритм работы которой выбирают таким образом, чтобы путем последовательного подключения источников Uэт.1 ÷ Uэт.т к сумматору установить приближенное равенство сигналов на входах 1 и 2 схемы сравнения. Подключение источников Uэт.1 ÷ Uэт.т производится через ключи, которые управляются импульсами опроса y1 ÷ yт сформированными генератором управляющих импульсов (ГУИ).

Соблюдение правильной последовательности срабатывания ключей обеспечивается логикой управления 3. Логика «наблюдает» за выходом схемы сравнения и в зависимости от двоичного сигнала «меньше» (когда U1 < U2) и «больше» (когда U1 > U2) управляет ключами, запоминает результаты сопоставления сигнала U1 = Uс и эталонов в каждом такте кодирования, устанавливает кодер в исходное положение. Таким образом, о величине сигнала Uс можно судить по состояниям ключей a ={0;1}. Взвешивание заканчивается, когда

Uс ≈  .

.

Формирователь кода 4 преобразует в последовательный код число

a1 a2…ат.

Рассмотренная структурная схема кодера последовательного действия (кодера с декодером в цепи ОС) самый простой по построению, но и самый худший как вариант, так как он требует т независимых источников Uэт, которые должны отличаться друг от друга точно в два раза.

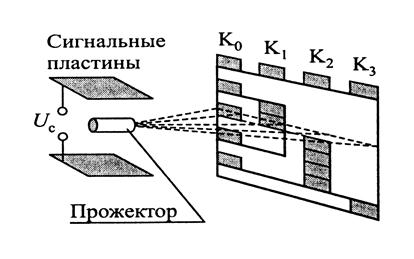

Линейные матричные кодеры построены на использовании матричного (кодового) поля, в котором отражены все возможные кодовые группы при данном числе разрядов кода. Кодовое поле может быть выполнено либо в виде набора решающих устройств, либо в виде кодовой матрицы в специализированной электронно-лучевой кодирующей трубке (рисунок 44).

Рисунок 44 – Матричный кодер параллельного действия

Матричные кодеры на сегодняшний день являются самыми быстродействующими. Однако они дороги, требуют высоковольтных напряжений, обладают невысокой стабильностью, поэтому их применяют только в специальных приборах.

| <== предыдущая страница | | | следующая страница ==> |

| Принцип дельта-модуляции в ЦСП | | | Кодирующие устройства с нелинейной шкалой квантования |

Дата добавления: 2014-09-10; просмотров: 1449; Нарушение авторских прав

Мы поможем в написании ваших работ!